# **LUMISTAR**

## LS-40-cP Bit Synchronizer Daughterboard

**Data Sheet**

## **Description:**

The Lumistar LS-40-cP Bit Synchronizer Daughterboard provides optimal reconstruction of a serial PCM data stream that has been corrupted by noise, phase jitter, amplitude modulation, or base line variations. The all-digital design assures a high performance, consistent product, with excellent reliability and long-term stability.

A unique Built-in-Test feature allows performance verification for the Bit Synchronizer to ensure the highest level of operation. *Auto-test BIT* is performed for a short duration on the application of power and tests more than 90% of the Bit Synchronizer components. This test verifies that power is properly applied, verifies that there are no internal bit errors, and performs other tests to ensure that the bit synchronizer is fully operational with status indication of results. *Command-test BIT* performs the same functions and can be initiated by the user at any time through the Lumistar software when used on Lumistar PC products. The user has the ability to generate internal

pseudo-random patterns and calculate internal bit error rates with or without the injection of forced errors. Various status indicators are also available through the software. The Bit Synchronizer also contains a BER reader as well as frame sync pattern indicator.

#### **Key Features:**

- PCM Data Rates up to 25 Mbps for NRZ-L (12.5 Mbps for Bi-Phase/Miller)

- Performance within 1 dB of theoretical to 10 Mbps (1.5 dB to 25 Mbps)

- All Digital Design ensures high reliability and long term performance

- Low power consumption

- Built-in-Test with internal BER measurement

## **Applicable Models:**

LS-40-cP25 Bit Synchronizer Daughter-board for data rates up to 25 Mbps LS-40-cP20 Bit Synchronizer Daughter-board for data rates up to 20 Mbps LS-40-cP10 Bit Synchronizer Daughter-board for data rates up to 10 Mbps

The Bit Synchronizer Daughter-boards can be installed on the LS-50-cP Compact PCI Multifunction PCM Decom. The Bit Synchronizer Daughter-boards are available on a PCI carrier (LS-40-P) or VME carrier (LS-40-V). The Lumistar LS-44-QBS incorporates 4 of the LS-40 Bit Synchronizer Daughter-boards in a 1U high rack mount chassis.

## **PCM Data Rate and Input Codes:**

The LS-40-cP Bit Synchronizers can operate over a range of 100 bits per second to their maximum data rates for all NRZ codes, or from 100 bits per second to half their maximum data rate for the Bi-Phase and Miller codes.

NRZ codes: NRZ-L, NRZ-M, NRZ-S RZ codes RZ

Split phase codes BI\$\phi\$-L, BI\$\phi\$-M, BI\$\phi\$-S Miller codes DM-M, DM-S, M\$^2\$-M, M\$^2\$-S Randomized codes RNRZ-L, RNRZ-M, RNRZ-S Randomization sequence: 2\$^{11}\$-1, 2\$^{15}\$-1, 2\$^{17}\$-1, 2\$^{23}\$-1

Lumistar, Inc. 3186 Lionshead Ave Ste 100 Carlsbad, CA 92010

PHONE: 760-431-2181 FAX: 760-431-2665 EMAIL: sales@lumistar.net www.lumi-star.com

Specifications are subject to change. Please verify the latest specifications at time of order.

### **Input and Signal Characteristics:**

Inputs signals: Single-ended or differential

Input Impedance: Shipped with  $75\Omega$ ,

$50\Omega$ , 1KΩ (Jumper Select)

Input Polarity: Auto-detect (normal or inverted) Input Signal Amplitude: 0.4 V pp to 10 V pp (nominal) Maximum Voltage Input:  $5 \text{V RMS for } 50 \Omega$  and  $75 \Omega$  Inputs

5V RMS for  $50\Omega$  and  $75\Omega$  Inputs 25V RMS for  $1K\Omega$  Impedance  $\pm$  5V for  $50\Omega$  and  $75\Omega$  Inputs;

Maximum DC Offset:  $\pm$  5V for 50Ω and 75Ω Inputs;  $\pm$  25 V for 1KΩ Impedance

Dynamic AC baseline: Baseline variations up to 100% of the input signal at rates to 0.1% of

the signal frequency for sinewave or sawtooth signals (100 Hz max)

#### **Phase-Locked Loop Performance:**

Loop-Bandwidth: Programmable from 0.01% to 2%

depending on the Bit Rate of the

input signal.

Acquisition Range: 0.04% to 8% depending on the

Loop-Bandwidth selected 0.1% to 20% depending on the

Loop-Bandwidth selected

#### **Bit Error Rate Performance:**

Tracking Range:

The LS-40 Bit Synchronizer performance relative to theoretical is indicated below when the applied signal has a S/N ratio within 1dB of the specified synchronization threshold with a Gaussian white noise bandwidth up to three times the bit rate, and has no jitter or base line variations on the input signal.

| Codes:    | Bit Rate:     | <b>Degradation from Theory:</b> |

|-----------|---------------|---------------------------------|

| NRZ       | <10 Mbps      | < 1 dB max (0.5 dB typical)     |

| NRZ       | 10 to 20 Mbps | < 1.5 dB max (1 dB typical)     |

| BΙφ, RΖ   | <5 Mbps       | < 1 dB max (0.5 dB typical)     |

| BΙφ, RΖ   | 5 to 10 Mbps  | < 1.5 dB max (1 dB typical)     |

| $DM, M^2$ | up to 10 Mbps | < 2 dB max (1 dB typical)       |

### **Capture Threshold:**

The Capture Threshold when the applied signal has a S/N ratio within 1 dB of the specified synchronization threshold, has a Gaussian white noise up to three times the bit rate, and has no jitter or base line variations on the input signal is defined below:

| Codes: | <b>Capture Threshold:</b> |

|--------|---------------------------|

| NRZ    | -1 dB (-3 dB typical)     |

| BI¢    | +1 dB (+0 dB typical)     |

The LS-40 Bit Synchronizer is capable of maintaining synchronization during periods of signal loss or during continuous periods of 1s or 0s lasting up to 245 bits in every 1024 bits, for NRZ coded signals up to 5 Mbps or BIφ coded signals up to 2.5 Mbps, providing:

- S/N ratio is greater than 12 dB

- PLL bandwidth is equal to 0.1%

- 50% Transition Density when the signal is present

- Input signal has no jitter or base line variations

- Signal has a constant amplitude

#### **Acquisition Time:**

The mean acquisition time is a function of the Loop Bandwidth and will be less than 100 bits with a Loop Bandwidth of 1% and less than 150 bits with a Loop Bandwidth of 0.1% for NRZ signals up to 5 Mbps or BI $\phi$  signals up to 2.5 Mbps, providing:

- Gaussian white noise in a band up to three times the bit rate

- Transition Density is greater than 2% of the bit rate

- Signal has no jitter or baseline variations on the input signal

#### **Output Signals:**

| Data              | TTL and RS-422 Driven         |

|-------------------|-------------------------------|

| Zero Degree Clock | TTL and RS-422 Driven         |

| Tape Outputs      | 1 V pp into 50 $\Omega$ (code |

|                   | programmable) TTL and RS-422  |

| Lock Status       | In Status Register            |

| Es/No >5dB Status | In Status Register            |

|                   |                               |

Input Signal Level Status

Built-in-test

Auxiliary Outputs/Inputs

(Consult Lumistar for use)

In Status Register

In Status

#### **Environmental:**

Temperature (Operating) 0 to 50 °C

Temperature (Non-Op) -25 to +70 °C

Humidity (Operating) 10% to 90% Non-Condensing

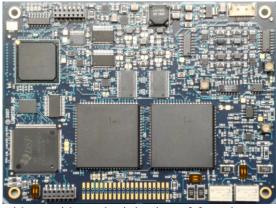

#### **Physical:**

Form Factor Daughterboard for LS-50-cP

3.6" x 4.8"

Power required (typical) 6.5 W total @ max data rate

800ma @ +5V (typical), 10ma @ +12V (typical), 200ma @ -12V (typical)

## **Synchronization Hold:**