Start your FPGA development project today! It’s never been easier than with the Acromag with the Zynq® UltraScale+™ MPSoC – The Ultimate FPGA Development Kit.

Firstly, the development kit is based on the AcroPack APZU mini PCIe FPGA series. It is a small yet powerful mezzanine module. It hosts a Zynq® MPSoC FPGA computing device. Perfect for I/O processing and Programmable Logic. Therefore, enabling designers to increase overall system performance. Simply by allocating the CPU and FPGA computing engines for different signal tasks. Making it a cost-effective form factor.

Benefits of the AcroPack APZU FPGA

- Small mezzanine module with power of Zynq MPSoC FPGA

- Integrated Multi core ARM processor and FPGA

- I/O and communication capabilities

- Rugged, high density, cost effective platform

- Xilinx® Zynq UltraScale+ MPSoC

- ARM Cortex™ A53 & R5 CPUs

- Programmable logic

- PCIe Bus Interface

Secondly, the FPGA Kit enables custom embedded computing – with reconfigurable FPGAs on Off the shelf Mezzanine Modules.

Did you know that user-configurable FPGA I/O modules offer the ability to create custom I/O boards? Simply download your own instruction sets into the I/O module’s FPGA. Then you can use your own application program to control the module’s analog or digital I/O channels for simulation, communication, diagnostics, image processing and other applications.

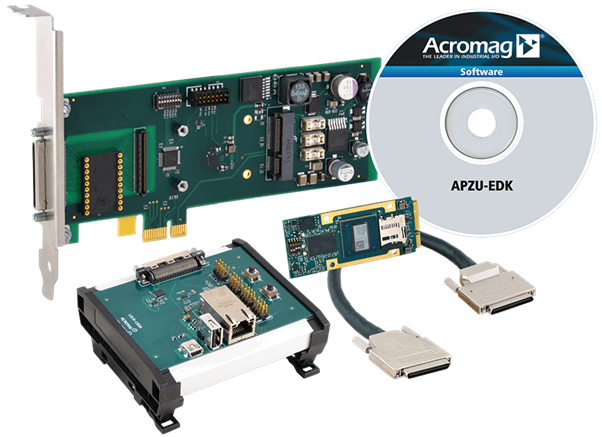

What you get in the FPGA Development Kit

AcroPack Configurable Zynq® UltraScale+™ MPSoC Module – choose one of these

- APZU-301-QSP = APZU-301 Module with 28 TTL channels

- APZU-303-QSP = APZU-303 Module with 20 TTL and 3 EIA-485/422 channels

- APZU-304-QSP = APZU-304 Module with 14 LVDS channels

APCe7012 Carrier Card whose features include:

- Acropack PCI Express Carrier Card

- Holds 1 x AcroPack Module

- The carrier JTAG port along with the provided JTAG programming cable access to APZU-30x JTAG interface

5028-626 Break Out Panel whose features include:

- I/O break out panel with cables for Ethernet, UART, JTAG and 68-pin carrier card connection

- The panel with mate directly to all 68-pin AcroPack Carriers.

- The break out panel and short 68-pin male to male 1 foot cable will bring an ethernet port, USB 2.0 ports, UART to USB port, digital I/O at jumper blocks and power and reset buttons out to the field

- The UART to USB port can be used with PuTTY to monitor APZU Zync development.

As well as the APZU-EDK Board Support Package and FPGA design kit. This includes an example of IP Block design, block RAM, system monitor and AXI interface to digital I/O

The Xilinx® Project files folder contains the PetaLinux and board definition files. These project files contain all the of the source files required to create Acromag’s example designs as described in the APZU-3xx user manual and APZU PetaLinux manual.

Download the spec sheet on the Ultimate FPGA development kit – Acromag-APZU-30x-QSP