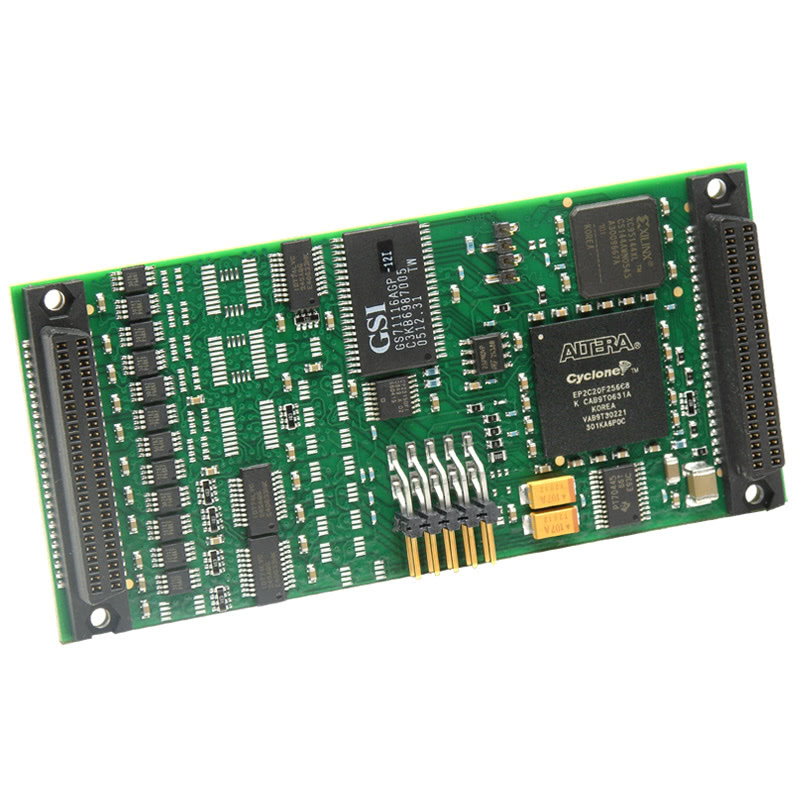

The Acromag IP-EP200 is an Altera FPGA with Digital I/O on an Industry Pack Module.

Firstly, the product is user customisable. It allows users to develop and store their own instruction set in the FPGA for adapting for different applications The FPGA on this module controls up to 48 TTL or 24 RS485 I/O Signals or mix of both types. Programs are downloaded through the JTAG port or via the IP bus directly to the FPGA.

An internal, pre programmed internal CPLD enables initialization. It acts as the bus controller during power up and whilst the program is downloading. Once the program downloads, the FPGA takes control of the Industry Pack (IP) bus and CPLD disable he FPGA on Acromag’s IP-EP200 modules can control up to 48 TTL or 24 RS485 I/O signals or a mix of both types.

Another model interfaces 24 LVDS I/O channels. User application programs are downloaded through the JTAG port or via the IP bus directly into the FPGA. A pre-programmed internal CPLD facilitates initialization by acting as the bus controller during power-up and while the program is downloading. This bus controller is limited to functions necessary for power-up and downloading. After the program downloads, the FPGA takes control of the IP bus and the CPLD disables.

Features of the Altera FPGA with Digital I/O IP-EP200 include:

- Altera Cyclone II EP2C20

- FPGA Four models available:

o IP-EP201: 48 TTL I/O lines

o IP-EP202: 24 differential RS485 I/O lines

o IP-EP203: 24 TTL and 12 RS485 I/O lines

o IP-EP204: 24 LVDS I/O lines

- FPGA programmable via JTAG port or IP bus

- Local static RAM (64K x 16) under FPGA control

- LVTTL external clock connected directly to the FPGA

- Supports 8MHz and 32MHz IP bus

- Programmable PLL-based clock synthesizer

- Example FPGA design code provided as VHDL

- o -8MHz IP bus interface

o Digital I/O control register

o others Hardware support for DMA and memory space

0 to 70°C (-40 to 85°C E models)

Finally, for more information, contact us.